逻辑门与CMOS晶体管

本文最后更新于 2025年3月31日 下午

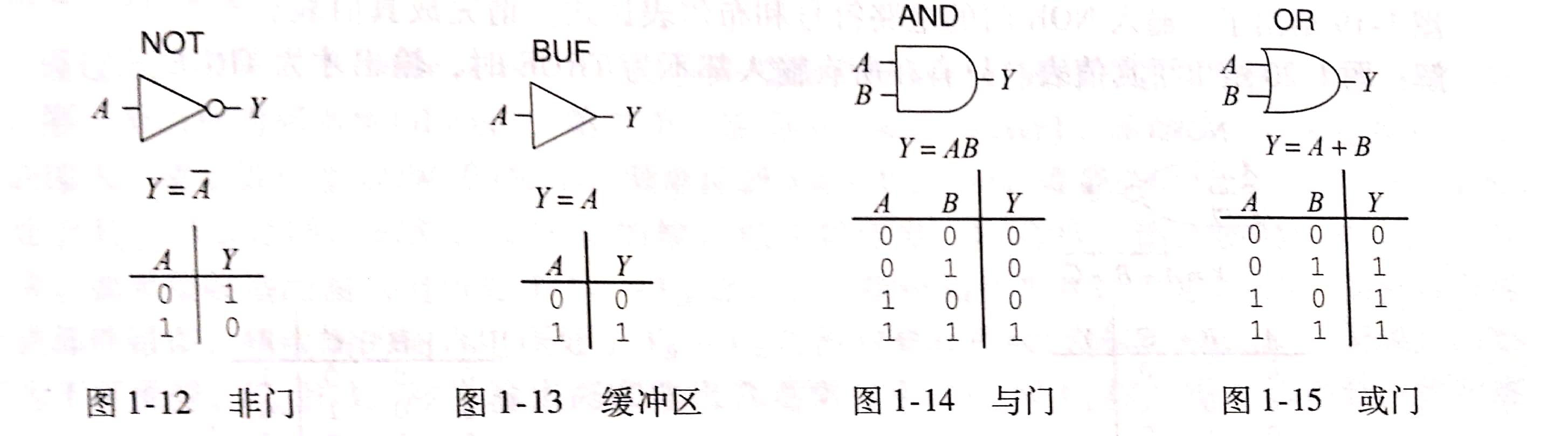

逻辑门

除此之外还有XNOR(同或), 三输入NOR门(NOR3)等。

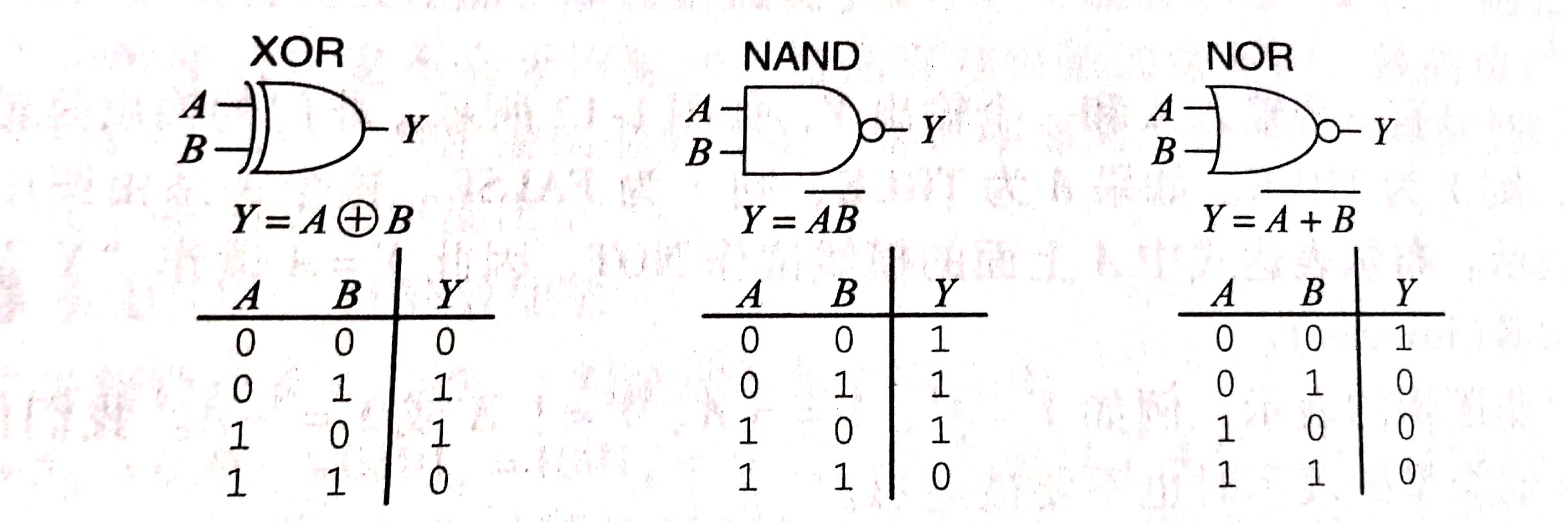

对电压的抽象

我们要将某一范围内的电压表示0,而另一范围内的电压表示1.例如一个5v的范围,我们用3.6v - 5v表示逻辑1,而0v - 2.4v表示逻辑0中间一部分既不表示0又不表示1。

由于电压会随运输而波动损耗,因此输出端的电压要比输入端的电压更为苛刻。

如图,左边就是输出端允许的电压范围,可以看见和右边都有一定差值,这个差值就是噪声容限。而右边输入端的电压经过调节,到了输出端电压范围又会变成左边那样。

这个调节实际上是晶体管本身的特性。

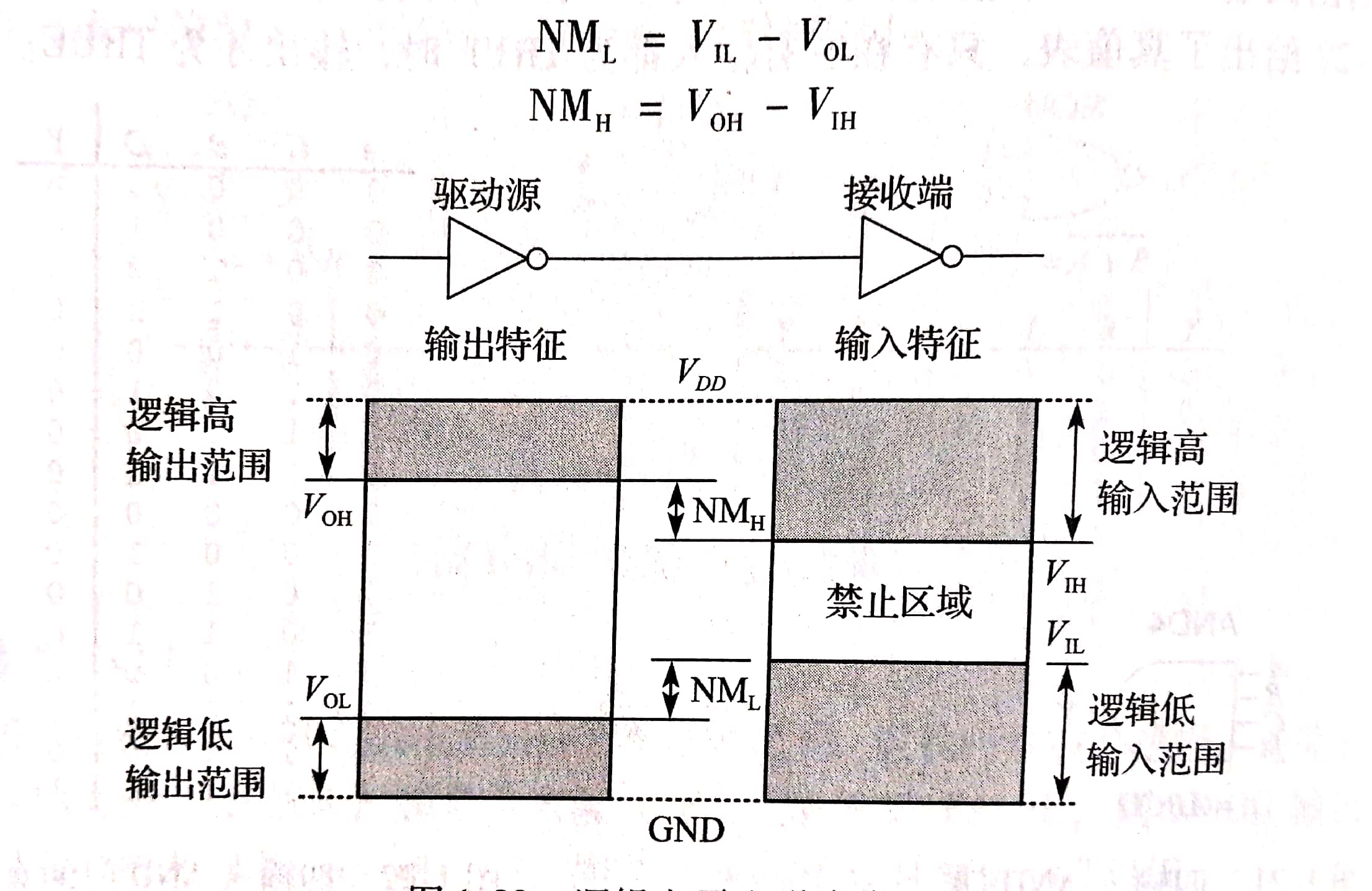

如图是非门的输入输出电压变化,其中A是输入,Y是输出。可以看到在$V{IL}$附近电压有一个大的跳跃,因此输入电压在$V{IL}$到$V_{IH}$之间是不可以的。

因此使用了一系列标准对逻辑高和逻辑低的范围进行了限制。

| 逻辑系列 | $V_{DD}$ | $V_{IL}$ | $V_{IH}$ | $V_{OL}$ | $V_{OH}$ |

|---|---|---|---|---|---|

| TTL(晶体管) | 5(4.75 - 5.25) | 0.8 | 2.0 | 0.4 | 2.4 |

| COMS(互补性金属-氧化物) | 5(4.5 - 6) | 1.35 | 3.15 | 0.33 | 3.84 |

| LVTTL(低电压) | 3.3(3 - 3.6) | 0.8 | 2.0 | 0.4 | 2.4 |

| LVCMOS | 3.3(3 - 3.6) | 0.9 | 1.8 | 0.36 | 2.7 |

CMOS晶体管

二极管

MOS晶体管主要由硅组成,硅最外层有4个电子,相互之间形成4对共价键达成稳定结构。但是这样的话就不导电了,因此掺杂一些其他元素如砷、硼等。

如果掺入砷(5个电子)那么就会多出一个电子,叫n型掺杂物。 如果掺入硼(3个电子),那么就会少一个电子从而出现空穴, 叫p型掺杂物.

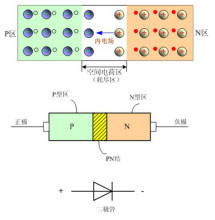

二极管就是一个n型区域和一个p型区域组合在一起形成的。

如图, n型区域和p型区域中间的电子和空穴会结合,从而使n型区域的原子带正电,p型区域带负电,产生了一个电场,这个电场会抑制空穴向n区移动,电子向p区移动,最终达到平衡状态。

空穴和电子结合的中间区域称作PN结

如果我们在p型区域通正电,n型区域通负电,那么产生的电场和内电场反向相反,当外电场超过一定值时(内电场通常0.7v)就会将内电场抵消从而让粒子移动而导电。

如果在n型区域通正电,p型区域通负电,那么会使NP结扩大从而更加不导电。

由于扩散现象,因此p区内也会有少量电子,n区内会有少量空穴,这些少量粒子称为少子,而多的粒子称为多子。由于少子的存在因此即使时n型区域通正电也会有小的电流。

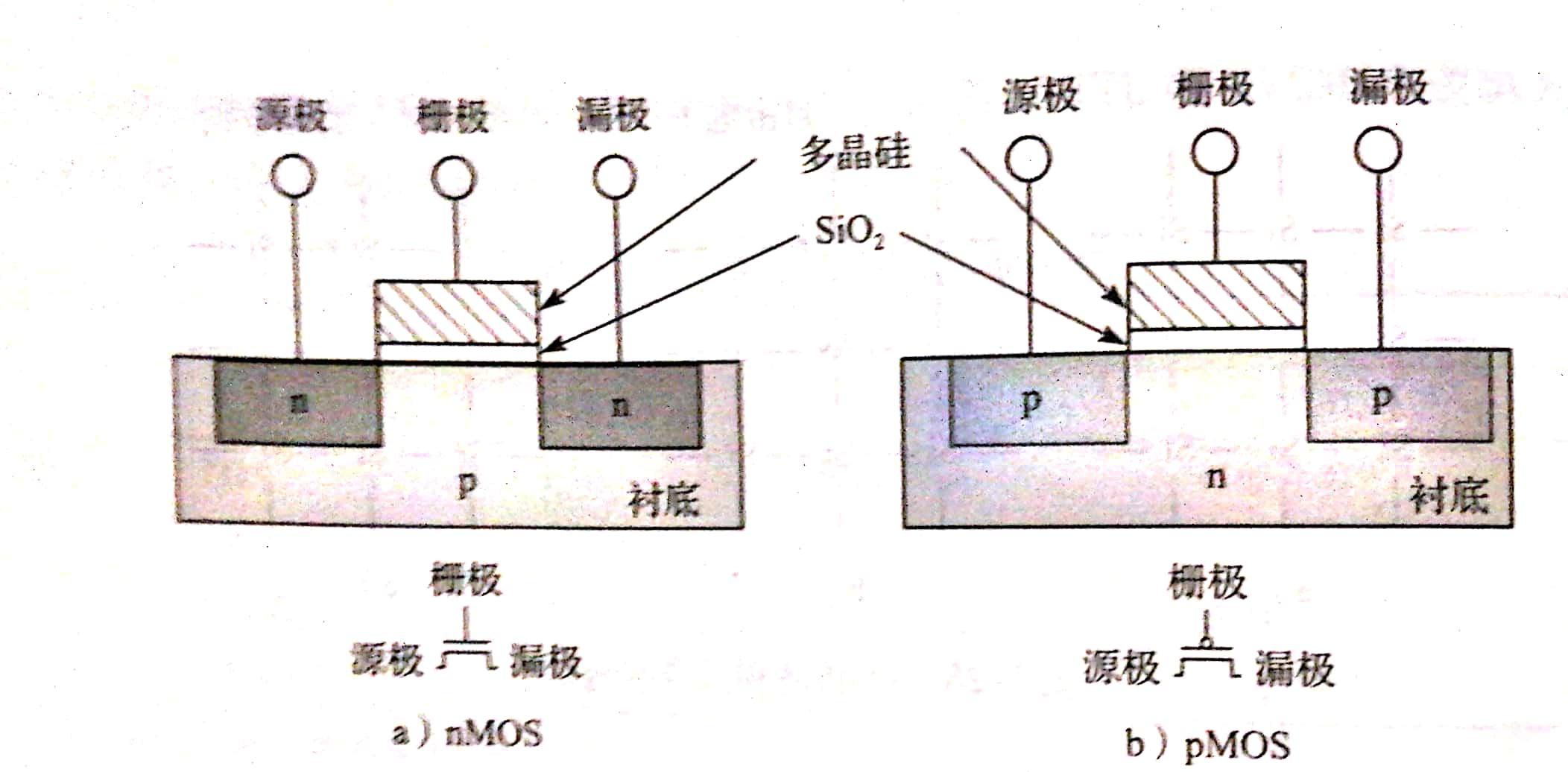

nMOS和pMOS

栅级就是我们控制的地方,它决定了源级和漏级是否有电流通过。(栅级下方还有一个电极)

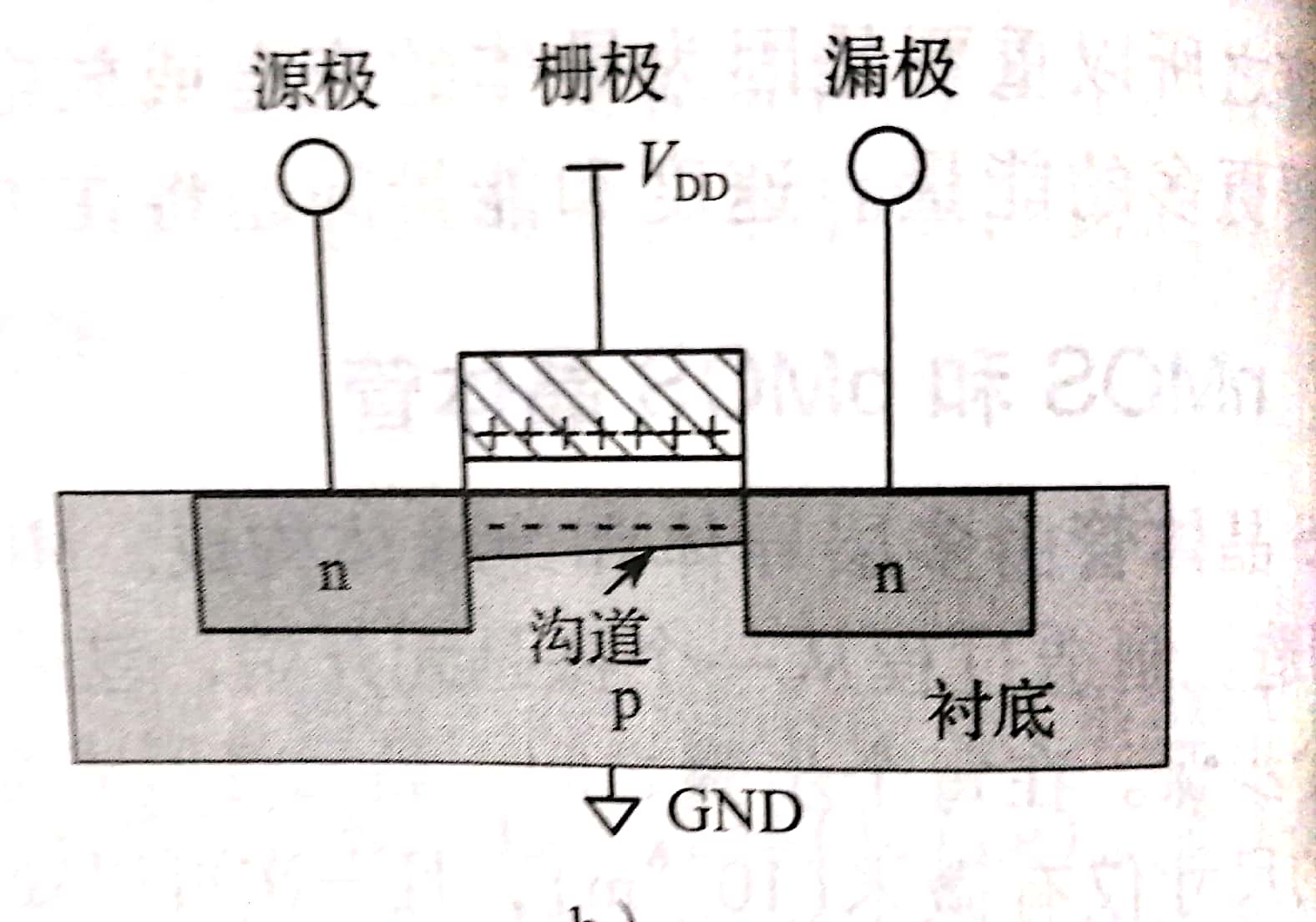

nMOS下方电极开始通低电压,当栅级通低电压时,二者没有电势差此时np结阻挡电流通过。

当栅级通高电压时,SiO2的下方会有大量的电子,将p型半导体的空穴填满并且转换成n型半导体,也就是说此时n型半导体是连通的,电流可以通过。

而pMOS下方开始是高电压,当上方低电压时连通,高电压时不能通过

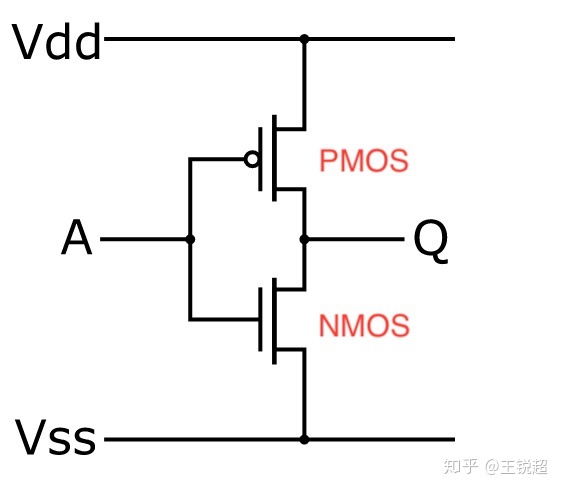

CMOS非门

如图 $V{dd}$ 是高电压, $V{ss}$ 是低电压。

如果A是低电压,则pMOS连通,nMOS不连通,也就是高电压可以通过,结果为1.

如果A是高电压,下方连通,结果为0.

如果上下方都有电流通过,则这个结果无效

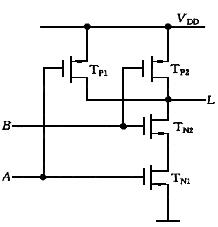

与非门

$T{p1}、 T{p2}$是pMOS, $T{n1}、 T{n2}$是nMOS

只要AB输入不同时为1,那么下方就不会连通,只要AB有一个是0,那么上方就会连通,也就是说

| A | B | 输出 |

|---|---|---|

| 1 | 1 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 0 | 0 | 1 |

与非门输出端加上一个非门就是与门。

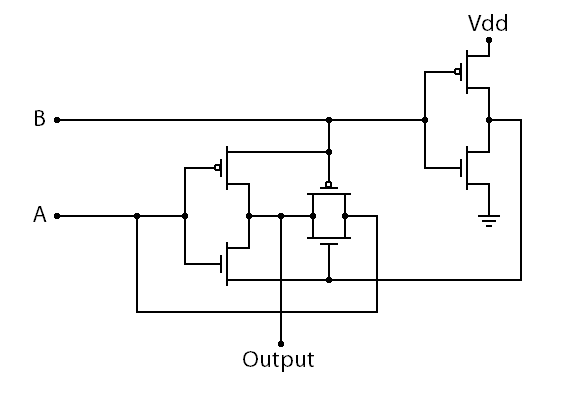

异或门

异或操作的表达式为:

异或门的结构如图所示,由一个反相器,一个传输门,一个cmos管组成。其中当B为0时传输门导通输出A,但是将传输门去除也可以实现功能,实际上最少只需要4个晶体管便可实现异或。当A为1时,输出为B的反向,当A为0时,输出为B。